MOnSter 6502 Runs BASIC!

July 6, 2016 7:03 pm MOnSter 6502Where we left off, the MOnSter 6502 had successfully ran a basic validation suite that validated a subset of the instructions but checked every bus cycle for accuracy. Shortly afterwards I was able to get it to run the full validation suite.

BASIC ran just fine after that. It was quite slow with a 6KHz clock but it was enough to run some simple BASIC programs. Typing was difficult because my validation computer uses an Atari POKEY chip to scan the keyboard, and it latches keystrokes very slowly because of the slow bus clock.

I’ve been experimenting with increasing the maximum clock frequency. It helped to reduce the bus capacitance that I added, but if I went too low, it cut into the minimum operating frequency. With less bus capacitance I was able to get the clock up to about 60KHz, and BASIC is quite usable at this speed.

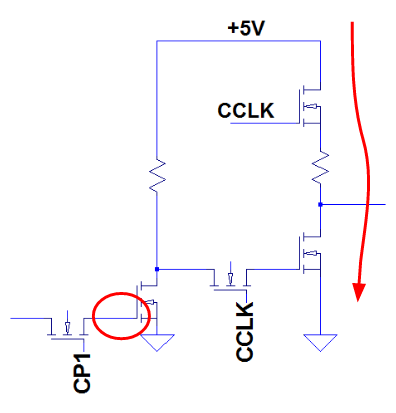

There is an issue I’ve been running into that has to do with the active bus pullups. The pullups are switched on by CCLK (first clock phase), and the pulldowns are normally changed on the CP1 edge (second clock phase). However this is done using a dynamic latch, so if the clock slows down too much, the latch will change state, causing both pullup and pulldown to be turned on at the same time. Here’s an example circuit:

The circled node is the storage node of the dynamic latch. If CP1 is off for too long, then this node can discharge, going from a ‘1’ to a ‘0’. When that happens, the output goes high and drives a ‘1’ into the pulldown transistor when CCLK goes high. CCLK turns on the pullup at the same time. As you can see in the diagram, I’ve added a small resistor in between both transistors to limit the current.

This resistor, although it protects the transistors, also limits the maximum clock speed by limiting how fast the bus capacitance can charge up.

I’ll be experimenting with some alternative ways of protecting the transistors without slowing down the bus too much.