Social Media Update

December 19, 2022 Uncategorized No CommentsFind my latest posts at Bluesky (https://bsky.app/profile/tubetime.bsky.social). I’ve also been active since 2022 on Mastodon as @tubetime@mastodon.social.

Find my latest posts at Bluesky (https://bsky.app/profile/tubetime.bsky.social). I’ve also been active since 2022 on Mastodon as @tubetime@mastodon.social.

Since it’s hard to search Twitter, I’ve put together a compilation of some of my best Twitter threads.

Welcome thread #1

Welcome thread #2

Micropodcast Episode 1

Dipped tantalum capacitor (my first cross section)

LMR-195 cable

Fiber optic cable

Undersea cable

Ethernet plug and jack

VGA cable

Type N connector

Type N connector (annotated)

Apple Magsafe connector

DVI single-link cable

Tantalum capacitor from Fluke 8400

BNC plug and jack

Flat phone cable

RIFA paper capacitor

SFP DAC cable

BGA package

USB-C connector

AC power cable

MAX233 chip

Another USB-C cable

Micro SD card

Magsafe 2 connector

DIP socket

Glass thermistor

DIP socket (machine pin)

Carbon composition resistor

Blown LED

Micro-D connector

Modern BGA SoC

MacBook power cable

HDBNC connector

Axial aluminum electrolytic capacitor

12AX7 vacuum tube

Slowly rotating and dramatically lit cutaway view of a 12AX7

12AX7 vacuum tube (behind the scenes)

2N2222 in a TO-18 metal can

Bi-color red/green LED

2N3904 transistor (TO-92)

1N914 diode

DE-9 plug and socket

Headphone plug and jack

Electrolytic capacitor

15-turn potentiometer

Audio transformer

BGA chip

Quartz crystal (HC-49)

Electret microphone element

LR44 alkaline button cell

Vibrator motor

DIP switch

Film capacitor

Inductor

Tact switch

Magnetic speaker

Slide switch

Ceramic chip capacitor

Reed relay

Polymer electrolytic capacitor

SMA connector

Ethernet transformer

LED

Prototype XL741 Kit

Fencing scoring machine

Zenith Minisport

HP125 keyboard reverse engineering

1982 DisplayPhone video call

Northern Telecom NT6K00AN DisplayPhone from 1982

MOS 6581 sound chip — aka the Commodore SID chip — slowly rotating and dramatically lit

slowly-rotating, dramatically lit Yamaha YM3812 OPL2 synthesizer chip

The KIM-1 lives!

Just wrote my first blink-an-LED program for this microcontroller, which is quite special…

Today i dug up my first mobile computing device. i bought this over 20 years ago. i wonder if it still works…

Two identical-looking Commodore mouses aren’t compatible. Why?

Epson HX-20 repair

Epson HX-20 thread

New Apple laptop this weekend. New to me anyway.

Fischertechnik robotics kit.

Prototype Connor IDE hard drive.

Atari 800 connected to modern PC

Rockwell AIM-65 computer with the MOnSter 6502!

GEOS on the C64.

Rebuilding a C64 power supply.

UNIX computer that uses audio cassettes for storage.

The Xerox Notetaker from 1978, the first computer to ever be used by a passenger on a commercial flight.

Say hello to the Intel SDK-86, the first computer to use the 8086 microprocessor!

AIM65 keyboard repair

Unusual keyboard keyswitch

There’s nothing quite like the ear piercing screech of a dot matrix printer generating a line full of ‘#’ symbols.

AIM-65 says hi

Cursed 3mm audio plug. Yes, it’s an Apple product.

35 years ago today, the Amiga 1000 was born!

Amiga 1000 secret RAM

Resurrection of an Amiga 2000 motherboard.

Commodore CDTV

Amiga 1200 RAM expansion

Swapping out 200-pin Amiga CPU connectors

New Amiga 3000

SOIC pin repair.

Amiga 4000 with Toaster Flyer

GVP RAM for Amiga 2000

Experiments with Toaster Flyer 4000

Amiga ROM adapters for 27C4096 EPROMs to 27C400-style ROM pinouts

Amiga 1000 ROM easter egg

Amiga 500 with a PC hidden inside

Extreme Amiga 4000 repair

Amiga Brataccas with unusual copy protected disk

Amiga ticking floppy drives

IBM PS/2 Model 95 computer experiments

IBM 7496 executive workstation video review

PCI versus microchannel slot

PS/2 floppy adapter thread

Installing OS/2 2.1 on the PS/2 model 50Z

OS/2 2.1 thread

Replacement plastic fasteners for IBM PS/2 systems

Field stripping my PS/2 Model 50Z

PS/2 model 50Z drive sled (3D print)

MCA bus experiments

Expanded memory card experiments

ISA bus IO_READY signal

Exploring the light pen

Experiments with 90MB Iomega Bernoulli cartridges

Rev A IBM 5150

Presenting a Targa video card from the mid 1980s

Experiments with the Targa 16 video card

Three monitors on an ISA bus computer

Graphics demos for the IBM EGA

Number Nine Revolution 512×8 graphics card from 1984. It was one of the first hardware accelerated cards available for the IBM PC!

Windows 95 UI book is *glorious*

Iomega’s Bernoulli box of 1982 was *not* the first floppy disk to use the Bernoulli principle.

Imaging Bernoulli cartridges.

The official IBM game control adapter has several unusual features.

Extreme 486 motherboard hacking.

Early MDA graphics cards could actually do color!

The original IBM PC had a cassette port

Found something strange on an 8″ floppy disk.

Metheus Ultra Graphics Accelerator 1104 has only two video modes: 1024×768 and emulated CGA at 960×600!

Extreme Sound Blaster 16 repair.

Unusual Okidata gm3315b 5 1/4″ floppy drive. It’s thin!

The Intersil IM6100 is a PDP-8 on a CMOS chip! What should I do with it?

Scopetrex build thread

Announcing the SCOPETREX — the vector gaming console for your oscilloscope or XY monitor!

Plaid Bib build thread

Plaid Bib announcement

Plaid Bib CPLD announcement

Snark Barker MCA engineering thread

Roland MPU-IMC card

Open-source clone of the IBM extender and receiver cards for the IBM 5161 expansion chassis!

IBM extender board thread

Announcing the Snark Barker MCA!

Wanted: your *broken* old Sound Blaster 1.0, 1.5, or 2.0 cards. That DSP needs to get dumped!

Snark Barker build thread

Clones of my Snark Barker SB 1.0 clone are apparently now available in Hong Kong.

A CDP1802 breadboard computer that starts simple and gets complicated

I made a controller for my Vectrex clone today!

Own an IBM PS/2 model 50, 50Z, or 70 with a broken proprietary floppy drive? Here’s a way you can make your own replacement out of some 3D printed parts and a standard PC floppy drive!

MOnSter 6502

MOnSter 6502 running validation program.

Fixing my Fluke 8400A digital voltmeter.

A look at my private stash of Nixie tubes!

One of the first digital voltmeters, the Fairchild 7100.

The bad tantalum cap in my frequency counter that started the cross section project

Power your Nixie tube with a coin cell!

One of my Nixie clocks that I built almost 13 years ago.

One of the world’s first electronic calculators, the Friden EC-130.

Testing vacuum tubes

Some unusual vacuum tubes

Using a VFD display as a triode

In 1959, GE tried to convince the world that vacuum tubes were better than transistors.

Oh look, it’s a vacuum tube module from a 1950’s IBM computer!

It’s tube time! well, time to sort and test some vacuum tubes.

A 120 year-old light bulb!

The Sony Watchman has a very weird “flat” CRT

Fired up my Sony Watchman today, and I actually found an analog TV broadcast

Check out this neat CRT display!

Playing with CRTs today. I can almost hear the sound effect this visualization pairs up with.

3D vector clock with three CRTs

A CRT with P7 long persistence blue/yellow phosphor

My friend’s TV pattern generator uses a tube called a Monoscope

First image from the Raytheon CK1414F10C Symbolray character generating tube.

Got a package dated June 28th, 1944.

Tidying up this tabletop Battlezone arcade machine I built

This cool 7-segment display uses neon instead of LEDs

Check out the archives of the Journal of the Society for Information Display.

Imagine it is 1935, and you’re trying to troubleshoot a circuit. How would you look at a voltage waveform?

Come to California Extreme! Come play my vector tabletop arcade games!

Don’t have a proper vacuum tube socket for a 7 or 8 pin miniature tube? Tear apart a solder cup DE-9 socket!

This is weird, someone is still broadcasting in UHF!

Do you remember that high-pitched whining sound that old school tube TVs used to make?

Let’s take apart this old TV camera!

This is the 26 x 72 foot (8 x 22m) crater resulting from the gas pipeline explosion in San Bruno in 2010.

This Tesla SUV ran into a traffic barrier at 70mph while on Autopilot. How could this happen?

This electrical transmission tower has a little problem. Can you spot it?

A tiny company nobody had heard of, Cadtrak, sued Commodore for patent infringement and won

All right, this is a new one. A EULA on…fruit?!

This happened to a Boeing 787 while it was parked at Boston Logan back in 2013

Celebrate Beethoven’s birthday by listening to this *remarkable* recording from 1944

Why does the schematic symbol of a bipolar transistor look the way it does?

Performing computations with DRAM

Some neat IC die photos

A very clever radio transmitter circuit

Investigating a tunnel diode

I once made a transistor out of a germanium diode and a guitar string

When the first IC chips came out, General Electric fired back, introducing the Compactron in 1961.

How did people simulate heat transfer, fluid flow, and electric fields before we had fast computers?

Repairing a vintage analog oscilloscope

Weird diodes

Wanna see an old telephone stepping relay in action?

Troubleshooting the pulse dialer on my Automatic Electric type 80.

Fixing my other logic analyzer, the HP1661A.

An incredibly rare transparent SOIC chip package.

Let’s talk about multipliers!

Here’s the Intel 1702, the first erasable, programmable read-only memory (EPROM) from 1971.

You’ve never seen this D-sub connector before!

D-sub connectors were invented in 1952 at Cannon by Sam Arson!

This neon lamp should never light up!

Parts inside parts

Here is part of the payload electronics from the Explorer 8 satellite (1960)!

I went to the first Bay Area Maker Faire back in 2006. Here are some of the photos

Today i finished building an AM radio for the @hackadayio circuit sculpture contest.

I decapped this LH0070 precision 10V reference, and found something unbelievable inside.

Some IC chips come in clear plastic. I picked up a tube today.

Let’s look at old school LED displays under a microscope.

Troubleshooting the STM32F407 USB bootloader

Let’s take apart this old chart recorder!

This is the uA702, the first commercial analog chip (an op-amp).

Here’s a fun little mystery! See this 2N2222A transistor…

Here’s an interesting part, the LM399H voltage reference.

This desk fan is 85 years old and still running strong. How would YOU design an electronics gadget to last 100 years?

Hey look it’s an ultra-rare transparent IC chip!

TIL about stakeless earth ground measurement.

It’s not always a software problem. It’s not always a hardware design problem.

Measuring propagation delays through buffers from different logic families.

Fixing a 1960s Japanese transistor radio.

Here’s a fun little cascaded Peltier cooler. Let’s see how cold it gets!

Time to visit the giant 2N696 in person!

You may have heard of an IC named after someone, but have you ever heard of a chip *pin* named after a dog?

Let’s read this @digikey catalog from 1987!

Illegal RC car!

Check out this cool prototype LED!

Discrete breadboard version of 555 timer

Around 1994 I built this voice recorder box with my grandfather. I wonder if it still works…

This is an EMP-20 device programmer from the early ’90s. it supports a huge variety of devices. The thing in the side that looks like a SIMM socket? It’s not…

Surprising facts about electrolytic capacitors

Altered chips

The first commercial product I ever designed

Here’s a nuclear battery in a DIP package.

PSA – Don’t store your chips in that black ESD foam!

Built a phono preamp

Why are chips often so expensive?

Reverse engineering the IR3E02 chip “DMG-REG” from several Game Boy variants.

Here’s the Snappy Video Snapshot. It is a video digitizer.

This computer has a really neat VGA BIOS screen with a shimmering rainbow

This is an LM168 voltage reference.

Time to extract some bits from this ROM image.

This is the chip layout of the famed Intel 80C51 showing all of the basic functional blocks.

Today I confirmed that I have a bit-accurate dump of the Sound Blaster CT-1351V202 DSP 2.02 firmware!

Sep 14, 2019

Aug 10, 2019

Jul 13, 2019

Jun 8, 2019

May 11, 2019

Apr 13, 2019

Mar 9, 2019

Sep 8, 2018

July 14, 2018

Apr 14, 2018

An off-brand capacitor failed on me, so I made a TV commercial

Here’s the new proposed USB-C connector.

I didn’t have a terminator for a 1/4″ audio jack, so I had to improvise…

Salesman: *slaps roof of 7805* this bad boy can fit so much magic smoke in it

What kind of sadist makes a breadboard that is 3 rows too short to fit a 40-pin DIP?

Since everyone’s reviewing emojis, let’s look at the light bulb emoji.

Aren’t D-sub connectors neat? Here is a DA-15 (bottom) along with a… hmm… hipster D-sub.

Saw the Jameco truck at Excess Solutions today.

Let’s order strange things from NIST! First up is this jar of reference peanut butter.

7 segment LED? Nixie tube?

Prototype 4″ floppy disk drive

Prototype BART ticket card with magnetic stripe

World’s first hard disk head

First prototype of the Hercules graphics card

I see your bit and byte, and I raise you a prototype head for the world’s first hard drive, the RAMAC.

This is a module from the IBM 4 Pi series aerospace computer. Not bad for 1972!

Here’s the wire-wrapped prototype of the original IBM PC (5150) motherboard!

The WeirdStuff sign has turned off for the last time. 🙁

WeirdStuff megathread: What’s your best memory of the place?

Vintage laptops at WeirdStuff!

Super clean IBM PC convertible at WeirdStuff

Yep, HSC is closing.

HSC electronics is up for sale.

HSC electronics sure was expensive back in the day.

The photo is HSC Electronics (their old building). The coffee machine was just to the left out of the frame.

HSC electronics has been sold to Excess Solutions!

HSC/Halted electronics featured in Newsweek, March 21, 1983

HSC Electronics sale today!

Last day for Halted

It looks like Amazon is buying a bunch of buildings, including the one occupied by Excess Solutions

At Excess solutions. Check out this wave solder machine!

My visit to Excess Solutions.

The orientation makes a difference when 3D printing something!

2020 Retrospective Thread

The Sound Blaster 1.0 was not the first PC sound card, but it was the first to support digital sound, two different types of sound synthesis, MIDI, and a joystick all in one card. Let’s lift the hood and examine how the card does its magic.

You can follow along by looking at the schematic here.

Sound Playback

There are three methods a Sound Blaster card uses to play back digital audio.

Direct DAC

The first is called Direct DAC and it means that the PC software has to feed the sound card each sample at just the right time. It works a lot like the parallel-port DACs that people used to build in the 80s and 90s, or like the Disney Sound Source. When you send a data byte to the sound card, it immediately changes the analog signal going into the speaker amplifier.

Software using this method typically sets up a periodic timer interrupt. In the interrupt handler, the new sample is calculated and then fed to the sound card for playback.

Although it’s a simple method, it produces extra noisy playback to due the timing jitter of the interrupt handler. Because PC interrupts are non-deterministic, the samples don’t occur at precisely the sampling rate. This timing difference means that the waveform being reproduced doesn’t match the source material, and the difference in voltage sounds like noise or hiss.

DMA DAC

The other method uses the DMA (Direct Memory Access) controller on the PC motherboard to automatically send samples to the sound card. It does require a little bit more work to set up the operation.

The next operations happen in a loop until all the samples have been played back. Notice that the software is not involved at all—just the DMA controller, the Sound Blaster, and main memory.

Finally, the Sound Blaster ends playback then triggers an interrupt to let the software know that it is done with playback.

Auto-Initialize DMA DAC

The final method, introduced with the Sound Blaster 2.0, is very similar to the previous method, except the ending. The Sound Blaster triggers an interrupt as before, but then it reloads the sample counter to the original value and continues requesting samples from the DMA controller!

The usual way software uses this feature is to create a seamless digital audio stream using a double buffer. The DMA controller gets a buffer that is twice as big as the number of samples that the Sound Blaster is programmed to play back. Because of that, the interrupt gets triggered halfway through buffer playback. In the interrupt handler, the software then loads a new set of samples into the buffer half that has already been played. When playback hits the end of the DMA buffer, the interrupt triggers again, only this time the software refills the last half of the DMA buffer. The DMA controller then wraps around to the beginning of the buffer and playback continues unbroken.

One of the side effects of this approach is that if the software crashes, the DMA controller and sound card continue to play back the sample buffer in a loop. You may have heard this when playing old DOS games back in the day.

Sound Recording

This works in very much the same way as playback including the Direct mode, DMA mode, and Auto-Init DMA modes, except data gets transferred in the opposite direction, from the sound card into main memory.

One interesting wrinkle is that the Sound Blaster doesn’t actually have a proper ADC (analog-to-digital converter)! Instead it uses a clever circuit and an algorithm to accomplish the same thing:

This technique is known as successive approximation, and it’s a technique used in many ADC chips. The code looks something like this:

mov p1,#80h ; Start DAC at the halfway point, 1000 0000

mov c,t1 ; 1 Put comparator output into carry bit

mov p1.7,c ; 2 If greater, then leave MSB as is. If less, clear MSB

setb p1.6 ; 1 Set DAC to upper or lower halfway point

mov c,t1 ; 1 Check comparator output again

mov p1.6,c ; 2 Rinse and repeat

setb p1.5

mov c,t1

mov p1.5,c

setb p1.4

mov c,t1

mov p1.4,c

setb p1.3

mov c,t1

mov p1.3,c

setb p1.2

mov c,t1

mov p1.2,c

setb p1.1

mov c,t1

mov p1.1,c

setb p1.0

mov c,t1

mov p1.0,c

mov a,p1 ; We are done, copy DAC code into accumulator.

The Hardware, Section By Section

Address Decoder

The address decoder takes the I/O port address off the ISA bus and looks for accesses at 210h, 220h, 230h, 240h, 250h, or 260h depending on the jumper setting. It also looks for 388h and 389h so that it can make the Yamaha OPL2 chip appear there for Adlib compatibility. It also decodes 0x200-207h as the joystick port (each address is actually the same).

A jumper, JP1, can be pulled to shut off the PC joystick port. The MIDI function still works, however. Many combo-IO boards came with a built-in joystick port so the one on the Sound Blaster may not always be needed.

Reset Circuit

It’s important to make sure the card powers up in a good state without generating spurious noises, so the SB uses the ISA RESET signal to clear the OPL2, the CMS chips, the joystick one-shot, and basically all of the other internal state latches.

There is also an IO port that, if you write a 1 to it, resets the DSP and its associated bus interface. (You also have to write a 0 to it afterwards to allow the DSP to start operating.) Later versions of the DSP require this to exit high speed auto-init DMA mode, since in this mode, the DSP devotes 100% CPU to servicing DMA requests.

DSP

The core of the digital sound capabilities of the Sound Blaster is the Digital Sound Processor, or DSP for short. It’s not actually a Digital Signal Processor in the traditional sense—it’s just an 8051 microcontroller with custom firmware.

The DSP also handles MIDI transmit and receive using the 8051’s built-in UART.

DSP Bus Interface

The bus interface allows the host PC to talk to the DSP. It uses two unidirectional 8-bit registers as a “mailbox,” temporary holding areas for a single data byte. One is for PC-to-DSP communications, and the other is for DSP-to-PC communications. There are also two data flip flops that are used to signal when data is available in one of the registers.

When the PC sends data to the DSP (I/O port 2XCh), the data gets stored in an 8-bit register and the flip-flop is automatically set high (DAV_DSP).

When the DSP reads the register, the flip-flop gets cleared automatically.

When the DSP sends data to the PC, the data goes into the other 8-bit register and the other flip-flop automatically gets set (DAV_PC). The PC can check this bit by reading from I/O port 2XEh. When it reads from I/O port 2XAh, it receives the byte of data and the flip-flop automatically gets cleared. The DSP can see that the PC has read the byte by checking the DAV_PC input. The DSP often checks this pin to make sure the PC has read a data byte before writing a new data byte to the register, otherwise the byte in the register will be lost before the PC has a chance to read it.

Interrupts

When the DSP is done with a particular (often lengthy) task, it can signal the host PC by asserting the interrupt line. It does this by pulsing IREQUEST which triggers a flip-flop that asserts the IRQ line on the PC bus. On the host PC, the interrupt handler is supposed to clear the interrupt by reading from I/O port 2XEh. This simply clears the flip-flop which then deasserts the IRQ line.

DMA

When the DSP needs a new sample from the PC (or needs to transfer a new sample to the PC during record mode), it pulses the DREQUEST line. Note that the DSP also needs to enable DMA by asserting its DMA_EN# line. When DREQUEST pulses, it causes the DMA request flip-flop to output a 1 on the DRQ1 line. The PC’s DMA controller responds by asserting DACK1#, which clears the flip-flop. DACK1# also bypasses the address decode logic of the Sound Blaster and forces it to either accept data from or place data on the ISA bus lines. This data transfer happens between the ISA bus and the mailbox registers.

Digital Audio Output

An 8-bit DAC connected to the 8051 generates an analog current corresponding with the digital code on its inputs. A current-to-voltage converter (U5C) changes the current into a voltage that is used by the rest of the circuit. This voltage goes through an antialiasing filter which removes distinctive- and ugly-sounding artifacts from the audio signal. U5A implements this filter using a Sallen-Key design. The filter cutoff frequency is about 4KHz, meaning that it’s designed to prevent aliasing for sample rates of 8KHz and above.

Next, the signal goes through an op-amp circuit which mixes the digital sound with the audio from the FM synthesis chip as well as the CMS chips. Unlike later Sound Blaster cards, the mixer is fixed and cannot be adjusted.

Finally, the signal goes through the volume control wheel and the built-in audio speaker amplifier before coming out the audio jack on the back of the card.

Since there is only one DAC, playback is mono, not stereo.

Audio Input

The Sound Blaster has a microphone jack on the back. It is only compatible with dynamic microphones or electret microphones that have built-in batteries because it has no bias power supply, unlike more modern sound interfaces. The input signal goes through a series DC-blocking capacitor and then into a preamplifier that converts the high impedance microphone signal into a low impedance signal needed by the rest of the internal circuit.

The preamplifier is also a Sallen-Key low-pass filter with a cutoff frequency of 4KHz. It is a 2nd order filter which means the attenuation increases by 40dB per decade. At 40KHz, the signal is down by 40dB.

The signal passes through a gain stage that amplifies the low-level signal, then passes it into the AGC (Automatic Gain Control) circuit. This circuit rectifies the AC input signal and filters it into a slow-moving voltage that represents the average level of the output (an envelope signal). This signal goes into a transistor that can attenuate the gain stage’s input signal level if it gets too high.

The gain stage uses an LM324 with a gain of 47 (about 17dB). Looking at the LM324’s datasheet, that gives us a bandwidth of about 30-50KHz. A small feedback capacitor (C41) makes this amplifier a single-pole low-pass filter with a cutoff frequency of 7.2KHz.

This filtered and amplified input signal goes into one input of the ADC comparator. The other comparator input comes from the audio DAC which generates the successive approximation signal.

There is something missing from the circuit, however. A true successive approximation ADC uses a sample-and-hold circuit to prevent the signal from changing voltage during an acquisition cycle. The Sound Blaster cheats and just pretends that the antialiasing filter will slow the signal down enough. It’s probably a bit noiser than it could be.

During ADC sampling, the DSP activates a mute circuit that prevents the successive approximation signal from bleeding out into the speakers, which is important because it would sound terrible! Because the audio DAC is used for both playback and recording, the Sound Blaster is only half duplex and cannot play back audio at the same time it is recording it.

MIDI I/O

The DSP, since it is just an 8051, has a built-in UART. The DSP firmware configures the UART for the MIDI baud rate (31250) and handles the MIDI messages.

There is a jumper bank just above the DSP that has some wires installed instead of a normal 0.1″ header pin array. The shorting wires route the UART RX and TX lines from the DSP out through the joystick connector. If the wires were removed, then a serial cable could be installed on the headers. I suspect this is how the engineers at Creative Labs debugged firmware issues.

To use the MIDI I/O with standard MIDI devices, you have to use a special adapter cable that includes the optoisolators required by the MIDI standard.

FM Synthesis

Two Yamaha chips produce FM-synthesized sound. The famous YM3812 OPL2 chip generates a digital serial PCM signal that gets converted into an analog waveform by the YM3014B DAC. The OPL2 chip has already been described extensively elsewhere.

One interesting thing is that the Sound Blaster uses two daisy-chained flip-flops to divide the ISA bus’s 14.318MHz clock signal down to 3.579MHz for use by the OPL2 chip.

To sum up, this part of the Sound Blaster behaves exactly like an Ad Lib sound card. Since there is only one single-channel YM3812, the FM synthesis output is mono.

CMS Music

The CMS (Creative Music System) chips are actually Philips SAA1099 audio chips.

The clock signal for these chips comes from a 7.159MHz signal which is just the ISA 14.318MHz clock divided by two. It’s a tap off the same clock divider chain used by the FM synthesis chip.

These two chips generate a left and a right channel, and they’re the only source of stereo sound on the Sound Blaster!

There is a flip-flop, U20B, that drives the ISA bus’s IO CHRDY signal to lengthen the host PC’s bus write cycle for the SAA1099 chips because they are quite slow.

Joystick Circuit

Here’s another place where the Sound Blaster cheats and doesn’t use an analog-to-digital converter. Just like the IBM joystick card (and clones), it uses an NE558 (the “quad” version of the classic 555 timer) as a variable one-shot timer. Each joystick axis is a variable resistor, that, along with a fixed capacitor in the Sound Blaster, controls a time delay. Writing to the joystick port triggers all four timers (one per joystick axis). The software then polls the joystick port and times how long it takes for each axis to reset. The time delay correlates with the position of the joystick.

In the above capture, the circuit has been connected to a resistance of 38.1K. Since the fixed capacitor is 0.01uF and the 558 threshold voltage is 2/3 of 5V or 3.33V, we get a time delay of about 420us.

Conclusion

The Sound Blaster 1.0 met a market need for a low-cost sound card with lots of features and backwards compatibility. It supported digital sampling using some clever hacks to keep the costs down, worked with all existing software that supported the Ad Lib sound card, and even integrated joystick support and MIDI functionality. No wonder the Sound Blaster series became the most popular sound card of all time!

If you want to try one out in your retro PC, consider building my replica design, the Snark Barker. The design files are available at my GitHub repository.

In December 1989, Creative Labs launched the now-famous Sound Blaster card. Almost 30 years later, I’d like to announce the Snark Barker, a replica of the original card designed to satisfy all your retrocomputing cravings!

Check out my GitHub repository for all the design files.

The design has been tested and works with a number of old DOS games, and is compatible with the CMS chips (actually Philips SAA1099 devices).

Ever wonder what the best op-amp in the world is? Wonder no more, it is the IC01 Ideal Operational Amplifier! Good luck buying one — they seem to be having some lead time issues.

Here’s another cloned card for your retro PC: may I present the MPU-IMC clone! (The what?)

It’s a clone of an old card that Roland made for interfacing PS/2 computers (MCA bus) with MIDI equipment like musical keyboards.

Files may be found at GitHub.

Don’t get too excited though because it’s not complete. Well, the board layout and schematic are fine, but there are two chips on the board that are special.

Anyway, I hope this is useful to someone out there!

Today is an exciting day for people who collect vintage IBM PCs and XTs! IBM had a somewhat obscure add-on product called the 5161 expansion chassis, which looked exactly like an IBM PC but with a difference case badge. It allowed customers to add two additional full-height drives (typically 10MB MFM hard drives) and 7 usable expansion slots (excluding the one used for the MFM disk controller). And yes, with those full-height hard drives, it sounded like a jet engine.

Connecting the expansion chassis to the host PC were two expansion cards. One, the extender, was placed in the host PC. The other, the receiver, went into the expansion chassis. A 62-pin D-sub connector tethered the two together.

One small problem: with the few remaining 5161 units, the extender card was typically separated and lost. Often the connecting cable was as well. If you got lucky, you might find a PC with the extender card still in it. Regardless, people often own more expansion chassis than extender cards, making them useless. Until now.

Based on careful study of high resolution photos of the cards and the schematics published in the IBM technical reference manuals, I’ve been able to design duplicates of both the extender and receiver cards. Details are in my GitHub repository.

Even if you don’t own an IBM 5161 (and I don’t blame you, it’s a bit obscure!), you might still find the cards useful. The receiver card works fine in common passive ISA backplanes! One small caveat: The backplane in the 5161 provides the 14.318MHz OSC signal which many ISA cards need. Passive backplanes do not provides this signal. You can check edge contact B30 on the back of the card edge. If there’s a missing contact or a contact that doesn’t connect to a trace, the card should work.

This card also needs some initialization to function. The BIOS in the PC/XT take care of this automatically, but this may not be true for all BIOSes. I’ve only tested it in my IBM PC. Even so, it may be possible to get it working by poking at the card’s I/O ports.

Enjoy!

Is such a thing possible?

Turns out it is, and it’s called a Monoscope. I recently got a Raytheon CK1414 Monoscope with a good getter and a working filament–naturally, I decided to fire it up.

The Monoscope is essentially a CRT; it has an electron gun and deflection plates which create a thin electron beam and points it towards the screen. Unlike a CRT, there is no phosphorescent coating on the end of the glass envelope. Instead, there is a metal plate that has an alphanumeric character set printed on it (an 8×8 array for 64 possible characters). There is also a conductive band around the glass called the collector which has a slight positive charge compared to the target. When the electron beam hits the target, secondary electrons “splash” off and are attracted to the collector. Fewer secondary electrons come off when the beam passes over part of the printed character. There is a wire coming out of the front of the tube that is attached to the target, and by measuring the current in this wire while you scan the electron beam across the target, you can pick up an analog video signal corresponding to the printed characters.

My early experimental setup suffered from a few problems (how do you focus the electron beam when you can’t see a spot on a phosphor screen?) but eventually I got this fuzzy image on my Tek 465M in XY mode:

You can see the round shape of the target along with some marks in the edges. The darker bit in the middle are characters, but things are just too fuzzy to see them. Part of the reason was that the video amplifier I used had a gain-bandwidth product of only 4.5MHz. In a non-inverting amplifier circuit with a gain of 100, the bandwidth was only about 45KHz! This just was not enough. There was also some distortion in the deflection amplifiers.

After adding another gain stage to the video amplifier and rearranging the circuit so that I could drive the deflection plates directly with some function generators, I saw this on my oscilloscope screen!

After a little research, I found out that the tube was used in some very early computer terminals including Raytheon’s DIDS-400 (c. 1967). To generate the display, the Monoscope was connected to a standard CRT. There were two sets of deflection circuits: one picked the character from the Monoscope while the other selected the location on the CRT. A pair of sine waves (really!) was fed to both sets of vertical and horizontal deflection plates, producing a raster scan which copied the character from one tube to another.

This worked quite well in the days before character generator ROMs. The tube acts essentially as an analog ROM.

Other companies combined both the Monoscope and the CRT into a single monster tube that had deflection plates, a mask with the character set, and a set of electromagnets that could rotate and position the character on the phosphor screen! Such a tube was called a Charactron(Convair) or Typotron(Hughes). A version of this tube was used in the computer terminals of the SAGE computer used in the US early warning radar system.

I decided to switch back to the higher-voltage deflection amplifiers to see if I could look at the entire character set at once. With the improved circuit, I got a better image:

It took a bit of tweaking to get the image. You can see alignment marks and other features on the metal target disk.

My setup looks like this:

In the middle there are three potentiometers which control brightness (really beam current), focus, and astigmatism.

As I was shutting off the high voltage supply, the image shrank on my oscilloscope screen since the deflection factor decreased, and I saw something interesting:

The target is in the middle, but there are odd shadows on the top, bottom, and sides. These are actually the deflection plates! The left and right plates are nearer to the electron gun so they block the view of the top and bottom plates which are closer to the target. When I saw this, I realized that this tube is essentially a miniature scanning electron microscope–only there’s just a single, permanent sample since the tube is sealed.

If you have one of these tubes and you want to experiment, the circuit I used looks like this (click for larger version):

You will need a 1000V power supply such as one designed for operating a photomultiplier tube. Needless to say, high voltages can kill you and should be treated with respect; please take proper precautions when experimenting with this stuff. Ground the metal cases of the potentiometers or use insulated knobs so you don’t shock yourself.

Connect the oscilloscope channels 1 and 2 (in XY mode) to the deflection plate inputs. Connect the oscilloscope’s Z-axis input to the video output from the amplifiers. I’ve only shown one stage, but you’ll need more gain to get a good signal. The function generators should be generating rising ramp sawtooth waveforms, but even sine waves will work. If you can synchronize the two, then you’ll get a more stable picture.

The vacuum tube’s filament needs 6.3VAC, so I’ve provided that with a transformer. Please check the transformer’s datasheet to make sure it can withstand the 1000V between the primary and secondary. Often this is called out as the maximum isolation voltage.

Well, there you have it–when ROM chips didn’t exist, people stored data in miniaturized scanning electron microscopes!

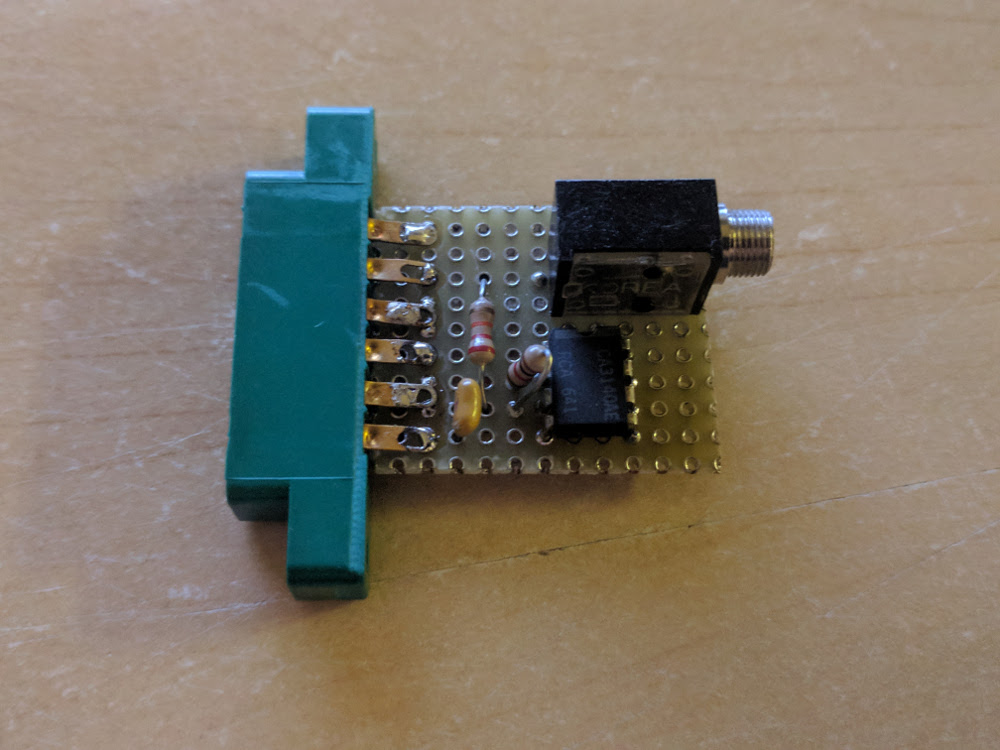

Before I put together a long term solution, I wanted a quick way to transfer software from my PC to my Commodore PET. There are other circuits, but I wanted something that used just one part.

The PET input is TTL level, so I needed something to go from audio level to TTL. Ideally a comparator circuit with plenty of gain. Well, I couldn’t find a decent comparator in my junk box, but I did find a CA3140 op-amp. This is way faster than I needed, but should work OK as a comparator. If you build this circuit, try to find a comparator or an op-amp with a rail-to-rail output.

And here’s what it looks like:

It works quite well. The circuit is not very sensitive to the output audio level from the PC–I set mine halfway (line level) and it was fine.

It’s been a while since we’ve had an update to the MOnSter6502 project–we’ve been very busy getting the second revision ready. At the same time, I’ve been designing a simple yet powerful 6502-based computer that can operate at the slow clock speeds required by the MOnSter6502.

But before I go into detail about that, take a look at this video update. It’s one thing to see photos of the MOnSter6502, but the video really brings out just how awesome this thing is in person! (Shameless plug for Maker Faire Bay Area 2017 where you should come visit us.)

The MOnSter6502 runs up to about 60KHz clock, which is quite a bit slower than the original. The computer I’ve designed for it uses another microcontroller to simulate hardware peripherals, inspired by capabilities of various ’80s computers and gaming consoles. The idea is to offload CPU-intensive video and sound tasks to the microcontroller, freeing up the 6502 so that it can be used in real time despite the slow clock.

Right now, I’ve implemented several software-defined peripherals

The computer can also run a full validation suite on the connected 6502, which has been quite useful troubleshooting the highly complex MOnSter6502 boards.

The computer is still a prototype, but you can see some shots of it in the video above.

You can find more updates and information at the project site.