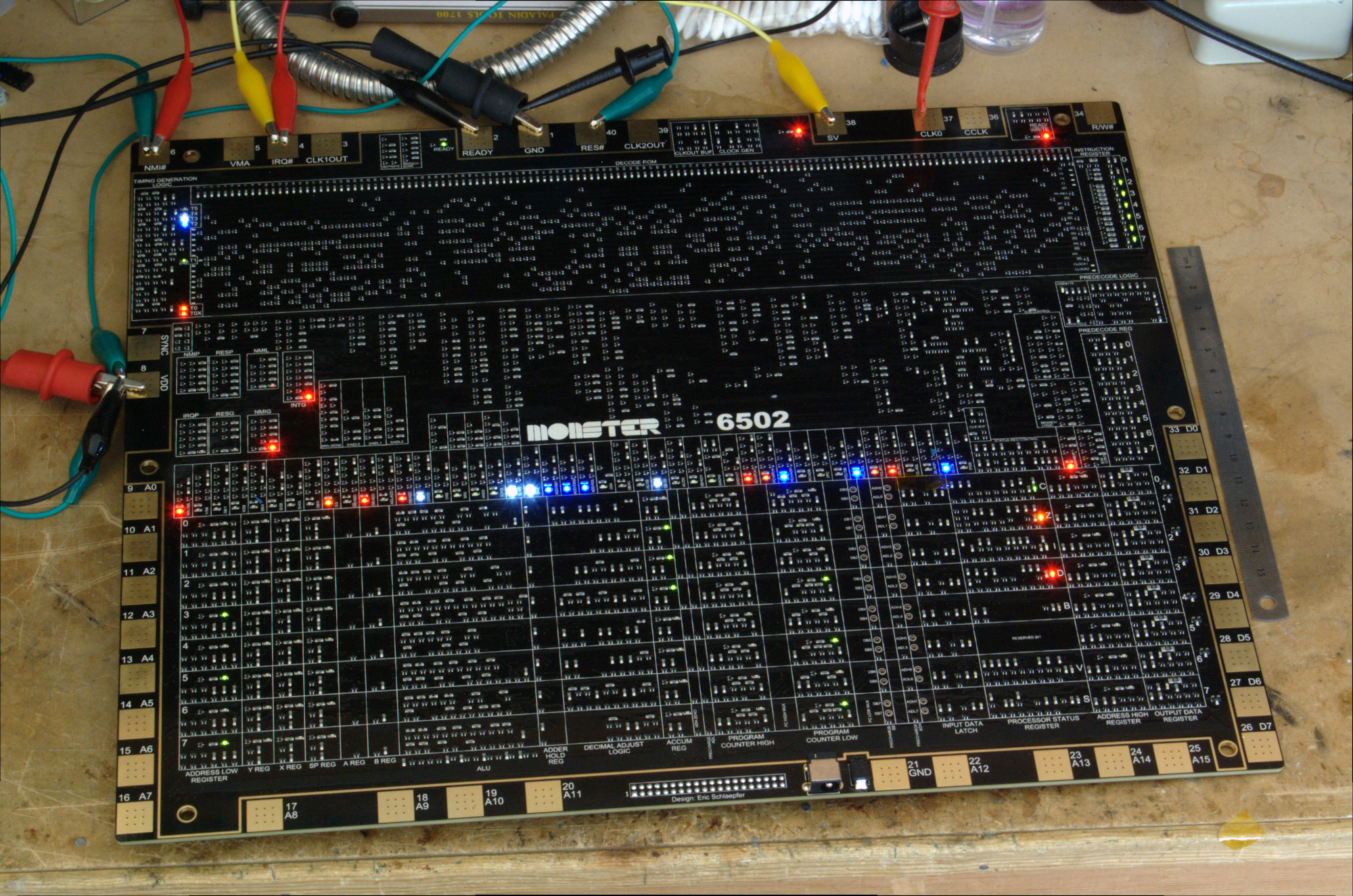

So, I made a thing. A really big thing. Really big and really crazy.

You might have seen my discrete 555 and 741 IC electronics kits. Well, a while back I had this idea about creating a discrete version of a microprocessor, but it just sounded too difficult, time consuming, or impractical. And part of me didn’t want to do it, because it just sounds so tedious to design–at every stage, I was secretly hoping to find a show-stopping problem. But part of me was really interested to see if it could be done.

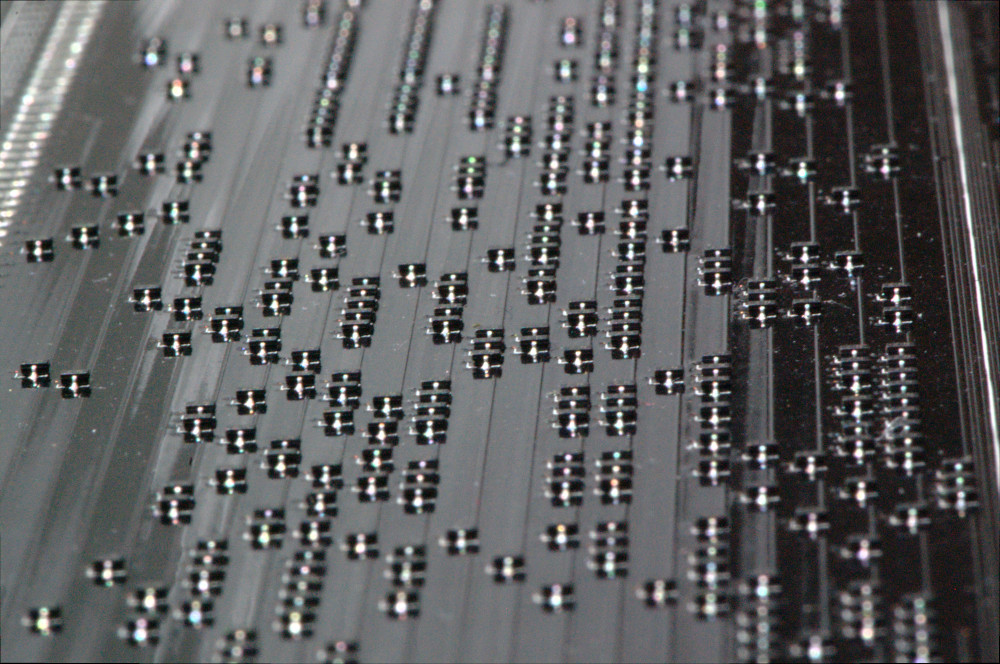

At dinner, Windell and I went through a thought experiment to see if it would even be possible. We weren’t sure how many transistors were in a 6502 (more than 1,000 but less than 10,000). If four surface mount transistors can fit in a square centimeter, then the board would need to be about 1,000 square centimeters, or about 32cm (13in) on a side, which is not as huge as we originally thought. Darn it, time to investigate further!

The hard work of reverse engineering the actual 6502 has already been done by the folks at Visual6502.org. I was able to extract the netlist from their Javascript simulation, which contains a list of all the transistors and every single wire connecting them together.

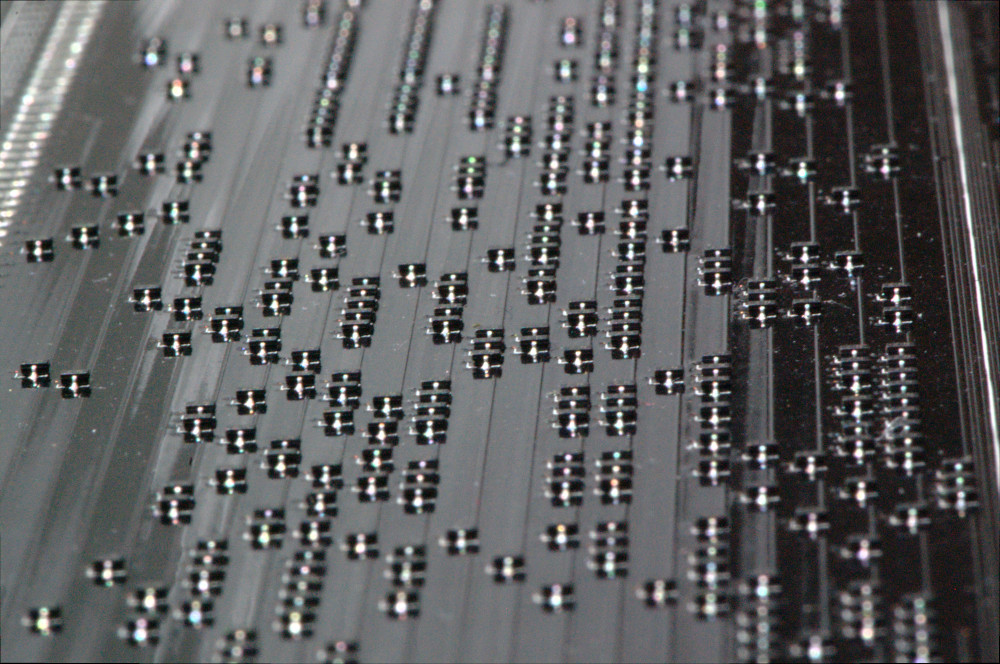

The 6502 uses dynamic NMOS logic, so it has a large number of “transmission gate” transistors that are used to switch currents. For various technical reasons, only a 4-terminal MOSFET can make an effective NMOS transmission gate. Those are really hard to find (nearly all MOSFETs are 3-terminal devices), but I found one–it’s an array of 4 MOSFETs on a single chip with a separate substrate pin.

I ran simulations using the transistors I found, and noticed that basic combinational logic and latches worked. I ordered parts and prototyped a few circuits. They worked perfectly.

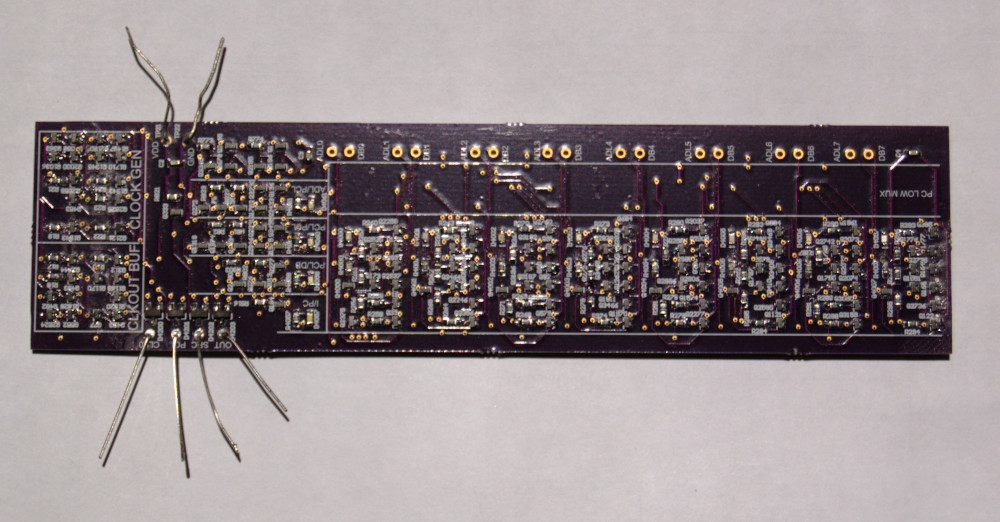

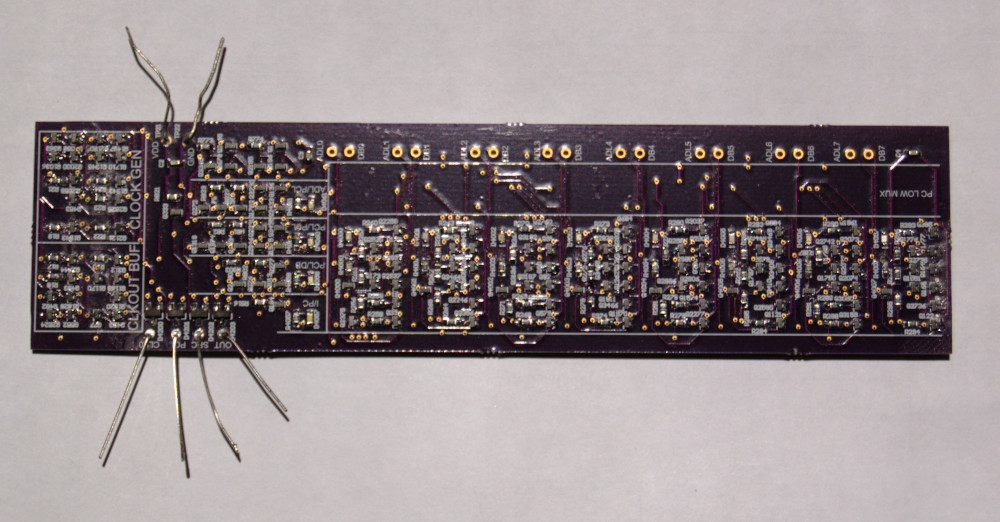

I designed and ordered an OSH Park circuit board with just 8 bits of the program counter register. I thought to myself that there was no way such a complex circuit could work, especially with the ripple carry propagation. Well, it worked.

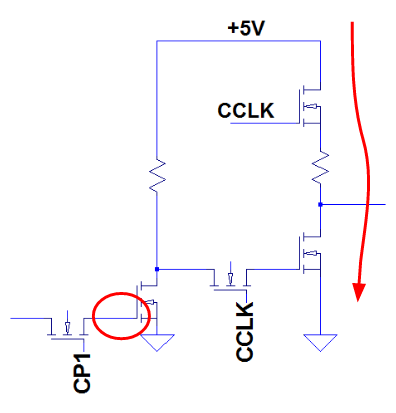

It was time to bite the bullet. I wrote a Python program that turned the Visual6502 netlist into a 3,510 line spreadsheet, and I began entering (on July 3, 2015) the transistors one by one into the schematic, highlighting each transistor as I finished it. Along the way, I noticed that the Visual6502 netlist had three extra transistors, T1088, T1023, and T3037.

(An example of an extra transistor)

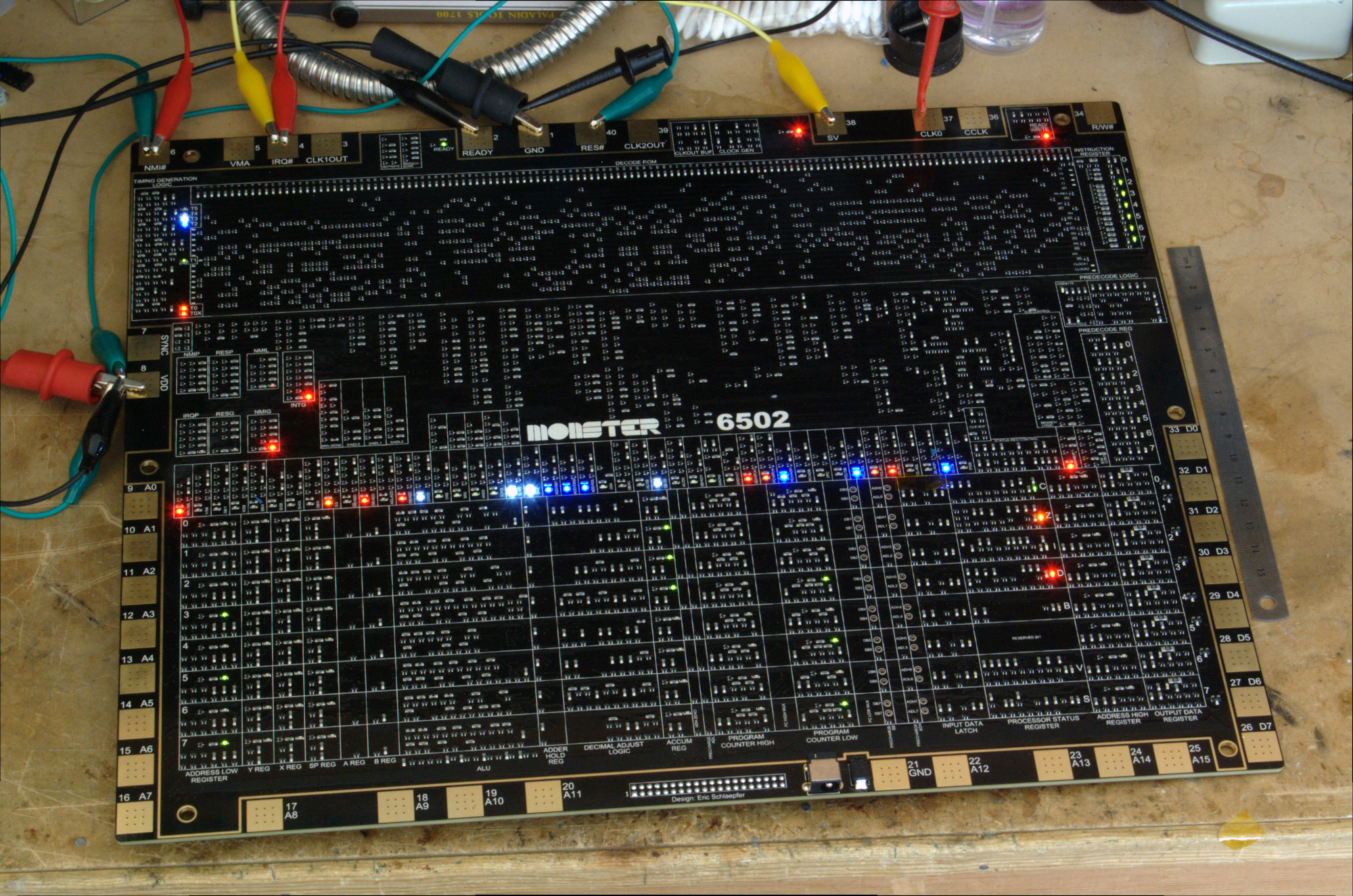

When I was done with all 61 pages, I wrote another Python program to compare my schematic against the original netlist and corrected a few mistakes. Then I added 167 colorful LEDs to various control lines and data bits, and a few protection components.

The layout came next. In the layout software, I placed 4,304 parts by hand and wired them up manually (no autorouter) over the course of several months, finishing the last transistor on Dec 1, 2015.

And last Thursday, the first boards came in. They are beautiful!

We’ll be bringing it to Maker Faire, so I have a week to work on bringup testing. Wish me luck!

You can find more details on the main project site, monster6502.com.